日报标题:USB 芯片原来静悄悄地干了好多事啊

ICantoo,苦逼IC入门菜菜菜鸟

ICantoo,苦逼IC入门菜菜菜鸟

意外发现知乎上还有这么专业的话题,哈,班门弄斧一下。

研究生两年 FPGA 学习,入职从事通信 SOC 芯片,碰巧同事离职,接手 USB。半年从完全不懂 USB,到完成第两颗芯片 USB2.0 前仿后仿验证,一颗 USB3.0 前仿后仿验证,支持第一个颗芯片 USB2.0 样片测试,牵头前同事遗留 USB3.0 测试。对 USB 算有些理解了,希望对关注者有帮助。

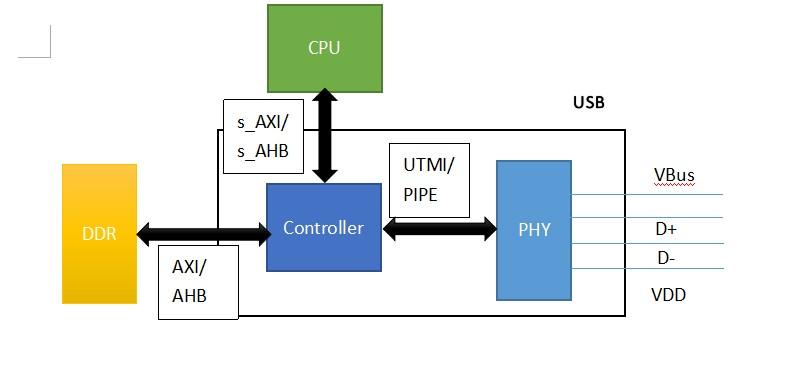

问题 1:上图,高速模块一般分为控制器 Controller 和 PHY 两部分,Controller 大多为数字逻辑实现,PHY 通常为模拟逻辑实现。

USB 芯片也分为 Controller 部分和 PHY 部分。Controller 部分主要实现 USB 的协议和控制。内部逻辑主要有 MAC 层、CSR 层和 FIFO 控制层,还有其他低功耗管理之类层次。MAC 实现按 USB 协议进行数据包打包和解包,并把数据按照 UTMI 总线格式发送给 PHY(USB3.0 为 PIPE)。CSR 层进行寄存器控制,软件对 USB 芯片的控制就是通过 CSR 寄存器,这部分和 CPU 进行交互访问,主要作为 Slave 通过 AXI 或者 AHB 进行交互。FIFO 控制层主要是和 DDR 进行数据交互,控制 USB 从 DDR 搬运数据的通道,主要作为 Master 通过 AXI/AHB 进行交互。PHY 部分功能主要实现并转串的功能,把 UTMI 或者 PIPE 口的并行数据转换成串行数据,再通过差分数据线输出到芯片外部。

USB 芯片内部实现的功能就是接受软件的控制,进而从内存搬运数据并按照 USB 协议进行数据打包,并串转换后输出到芯片外部。或者从芯片外部接收差分数据信号,串并转换后进行数据解包并写到内存里。

问题 2:FPGA 不使用 USB 芯片或者硬核的话,必须用 FPGA 逻辑资源实现图 1 图中 Controller 部分,外加 PHY 芯片,软件再按照协议实现对 USB 的控制。如果有 USB 芯片,则只需实现软件控制部分。软件控制部分协议 USB 1.1 UHCI/OHCI,USB 2.0 EHCI, USB 3.0 XHCI。